2.4 Common Drain Amplifier

The common drain amplifier is analogous to the common collector emitter follower. The JFET version is also known as a source follower. The prototype amplifier circuit with device model is shown in Figure 2.4.1 . As with all voltage followers, we expect a non-inverting voltage gain close to unity, a high 𝑍𝑖𝑛 and low 𝑍𝑜𝑢𝑡.

The input signal is presented to the gate terminal while the output is taken from the source. Many bias circuits may be used here as long as they do not have a grounded source terminal such as constant voltage bias.

Voltage Gain

In order to develop an equation for the voltage gain, 𝐴𝑣, we follow the same path we took with the common source amplifier earlier in this chapter. First, we start with the fundamental definition, namely that voltage gain is the ratio of 𝑣𝑜𝑢𝑡 to 𝑣𝑖𝑛, and proceed by expressing these voltages in terms of their Ohm’s law equivalents.

![]()

(2.4.1)

Equation 2.4.1 is very similar to the gain equation derived for the swamped common source amplifier; the notable changes being the lack of the minus sign indicating that this circuit does not invert the signal, and 𝑟𝐿 replacing 𝑟𝑆 in the denominator. It is worth remembering that 𝑟𝐿 here is the AC source resistance while in the common source amplifier 𝑟𝐿 is the AC drain resistance. To avoid potential confusion, this equation could also be written as

![]()

(2.4.2)

In any event, the goal is to make sure that 𝑔𝑚𝑟𝑆≫1 . By doing so, the voltage gain will be very close to unity.

Input Impedance

The analysis for common drain input impedance is virtually identical to that for the swamped common source amplifier. The result is replicated here for convenience.

![]()

(2.4.3)

Output Impedance

In order to investigate the output impedance, we’ll separate the load resistance from the source bias resistor, as shown in Figure 2.4.2.

From the position of 𝑅𝐿, looking back toward the source we find 𝑅𝑆 in parallel with the impedance looking back into the source terminal. The voltage at this node is 𝑣𝐺𝑆 and the current entering this node is 𝑖𝐷. The ratio of the two must yield the impedance looking into the source.

![]()

![]()

![]()

(2.4.4)

Therefore, the output impedance is

![]()

(2.4.5)

We can expect this value to be much smaller than the output impedance of typical common source amplifiers.

Example 2.4.1

For the follower shown in Figure 2.4.3 , determine the input impedance and output voltage. Assume 𝑉𝑖𝑛=100 mV, 𝐼𝐷𝑆𝑆=30 mA, 𝑉𝐺𝑆(𝑜𝑓𝑓)=−2 V.

This is a follower using self bias. We’ll find 𝑔𝑚 via the self bias graph.

![]()

![]()

![]()

𝑅𝑆 is 1 k Ω , yielding 30 for 𝑔𝑚0𝑅𝑆 . The normalized drain current from the self bias graph is approximately 0.05.

![]()

![]()

![]()

![]()

![]()

![]()

Thus 𝑉𝑜𝑢𝑡 is 71.6 mV. By inspection, 𝑍𝑖𝑛 may be approximated as 2.2 M Ω .

Example 2.4.2

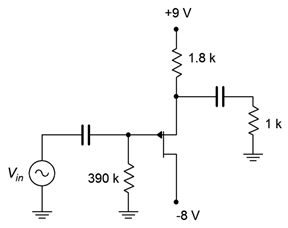

For the circuit shown in Figure 2.4.4 , determine the input impedance and output voltage. Assume 𝑉𝑖𝑛=100 mV, 𝐼𝐷𝑆𝑆=36 mA, 𝑉𝐺𝑆(𝑜𝑓𝑓)=3 V.

This follower uses combination bias with a P-channel JFET. Note that the source is at the top. We’ll find 𝑔𝑚 via the combination bias graph for 𝑘=3 ( 𝑘=𝑉𝑆𝑆/𝑉𝐺𝑆(𝑜𝑓𝑓)) .

![]()

![]()

![]()

𝑅𝑆 is 1.8 kΩ, yielding 43.2 for 𝑔𝑚0𝑅𝑆. The normalized drain current from the 𝑘=3 combination bias graph is approximately 0.17.

![]()

![]()

![]()

![]()

![]()

![]()

Thus 𝑉𝑜𝑢𝑡 is 86.4 mV. By inspection, 𝑍𝑖𝑛 may be approximated as 390 k Ω .