7.6 The Differential Amplifier

Most modern operational amplifiers utilize a differential amplifier front end. In other words, the first stage of the operational amplifier is a differential amplifier. This circuit is commonly referred to as a diff amp or as a long-tailed pair. A diff amp utilizes a minimum of 2 active devices, although 4 or more may be used in more complex designs. Our purpose here is to examine the basics of the diff amp so that we can understand how it relates to the larger operational amplifier. Therefore, we will not be investigating the more esoteric designs. To approach this in an orderly fashion, we will examine the DC analysis first, and then follow with the AC small signal analysis.

DC Analysis

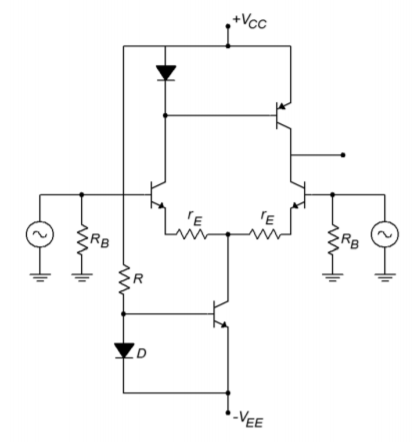

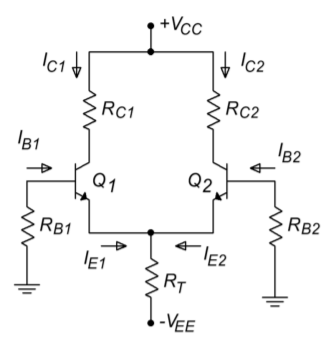

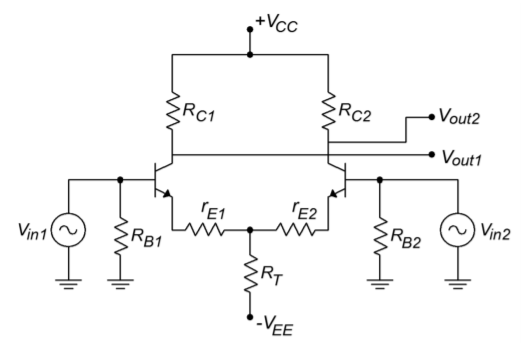

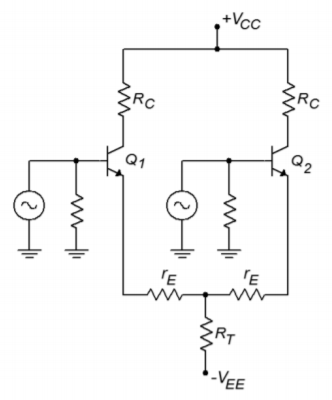

A simplified diff amp is shown in Figure 7.6.1 . This circuit utilizes a pair of NPN bipolar transistors, although the circuit could just as easily be built with PNPs or FETs. Note the inherent symmetry of the circuit. If you were to slice the circuit in half vertically, all of the components on the left half would have a corresponding component on the right half. Indeed, for optimal performance, we will see that these component pairs should have identical values. For critical applications, a matched pair of transistors would be used. In this case, the transistor parameters, such as 𝛽 , would be very closely matched for the two devices.

In Figure 7.6.2 , the circuit currents are noted, and the generalized current source has been replaced with a resistor/negative power supply combination. This is in essence, an emitter bias technique. Assuming that the base voltages are negligible and that 𝑉𝐵𝐸 is equal to 0.7 V, we can see that the emitter of each device is at approximately -0.7 V. Kirchhoff’s Voltage Law indicates that the bulk of the negative supply potential must drop across 𝑅𝑇 .

![]()

Knowing this, we may find the current through 𝑅𝑇 , which is known as the tail current, 𝐼𝑇 .

![]()

If the two halves of the circuit are well matched, the tail current will split equally into two portions, 𝐼𝐸1 and 𝐼𝐸2 . Given identical emitter currents, it follows that the remaining currents and voltages in the two halves must be identical as well. These potentials and currents are found through the application of Kirchhoff’s Voltage and Current Laws just as in any other transistor bias analysis.

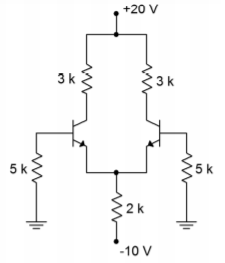

Example 7.6.1

Find the tail current, the two emitter currents, and the two collector to ground voltages in the circuit of Figure 7.6.3 . You may assume that the two transistors are very closely matched.

The first step is to find the tail current:

![]()

The tail current is the combination of the two equal emitter currents, so

![]()

![]()

![]()

If we make the approximation that collector and emitter currents are equal, we may find the collector voltage by calculating the voltage drop across the collector resistor, and subtracting the result from the positive power supply.

![]()

![]()

![]()

![]()

Again, because we have identical values for both halves of the circuit, 𝑉𝐶1=𝑉𝐶2 . If we continue with this and assume a typical 𝛽 of 100, we find that the two base currents are identical as well.

![]()

![]()

![]()

Noting that the base currents flow through the 5 k Ω base resistors, we may find the base voltages. Note that this is a negative potential because the base current is flowing from ground into the transistor’s base.

![]()

![]()

![]()

This result indicates that the actual emitter voltage is closer to -0.8 V than -0.7 V, and thus, the tail current is actually a little less than our approximation of 4.65 mA. This error is probably within the error we can expect by using the 0.7 V junction potential approximation.

Input Offset Current and Voltage

As you have no doubt guessed, it is impossible to make both halves of the circuit identical, and thus, the currents and voltages will never be exactly the same. Even a small resistor tolerance variation will cause an upset. If the base resistors are mismatched, this will cause a direct change in the two base potentials. A variation in collector resistance will cause a mismatch in the collector potentials. A simple 𝛽 or 𝑉𝐵𝐸 mismatch can cause variations in the base currents and base voltages, as well as smaller changes in emitter currents and collector potentials. It is desirable then to quantify the circuit’s performance so that we can see just how well balanced it is. We can judge a diff amp’s DC performance by measuring its input offset current and its input and output offset voltages. In simple terms, the difference between the two base currents is the input offset current. The difference between the two collector voltages is the output offset voltage. The DC potential required at one of the bases to counteract the output offset voltage is called the input offset voltage (this is little more than the output offset voltage divided by the DC gain of the amplifier). In an ideal diff amp all three of these factors are equal to 0. We will take a much closer look at these parameters and how they relate to operational amplifiers in later chapters. For now, it is only important that you understand that these inaccuracies exist, and what can cause them.

AC Analysis

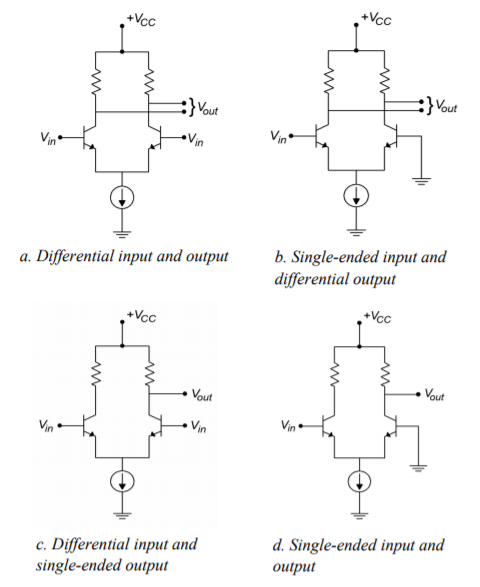

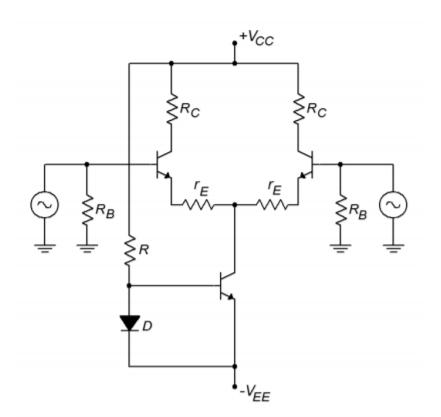

Figure 7.6.4 shows a typical circuit with input and output connections. In order to minimize confusion with the DC circuit, AC equivalent values will be shown in lower case. Small emitter degeneration resistors, 𝑟𝐸1 and 𝑟𝐸2, have been added to this

diff amp. This circuit has two signal inputs and two signal outputs. It is possible to configure a diff amp so that only a single input and/or output is used. This means that there are four variations on the theme:

- Differential (also called dual- or double-ended) input, differential output.

- Differential input, single-ended output.

- Single-ended input, differential output.

- Single-ended input, single-ended output.

These variations are shown in Figure 7.6.5 . For use in operational amplifiers, the differential input/single-ended output variation is the most common. We will examine the most general case, the differential input/differential output version.

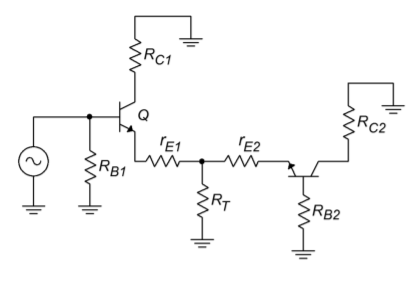

Because the diff amp is a linear circuit, we can use the principle of Superposition to independently determine the output contribution from each of the inputs. Utilizing the circuit of Figure 7.6.4 , we will first determine the gain Equation from 𝑉𝑖𝑛1 to either output. To do this, we replace 𝑉𝑖𝑛2 with a short circuit. The AC equivalent circuit is shown in Figure 7.6.6 .

For the output on collector 1, transistor 1 forms the basis of a common emitter amplifier. The voltage across 𝑟𝐶1 is found via Ohm’s Law.

![]()

The negative sign comes from the fact that AC ground is used as our reference. (i.e., for a positive input, current flows from AC ground down through 𝑟𝐶1 , and into the collector.) To a reasonable approximation, we can say that the collector and emitter currents are identical.

![]()

We must now determine the AC emitter current in relation to 𝑉𝑖𝑛1 . In order to better visualize the process, the circuit of Figure 7.6.6 is altered to include simplified transistor models, as shown in Figure 7.6.7 .

𝑟′𝑒 is the dynamic resistance of the base emitter junctions and is inversely proportional to the DC emitter current. You may recall the following Equation from your prior course work:

![]()

Where

𝑟′𝑒 is the dynamic base-emitter junction resistance,

𝐼𝐸 is the DC emitter current.

For typical circuits, the values of 𝑟′𝑒 and 𝑟𝐸 are much smaller than the tail current biasing resistor, 𝑅𝑇 . Because of its large size, we can ignore the parallel effect of 𝑅𝑇 . By definition, the AC emitter current must equal the AC emitter potential divided by the AC resistance in the emitter section. If you trace the signal flow from the base of transistor 1 to ground, you find that it passes through 𝑟′𝑒1 , 𝑟𝐸1 , 𝑟′𝑒2 and 𝑟𝐸2 . You will also notice that the magnitude of 𝑖𝐸1 is the same as 𝑖𝐸2 , although they are out of phase.

![]()

Because the circuit values should be symmetrical for best performance, this Equation may be simplified to

![]()

If we now solve for voltage gain,

![]()

![]()

![]()

![]()

Where

𝐴𝑣 is the voltage gain,

𝑟𝐶 is the AC equivalent collector resistance,

𝑟𝐸 is the AC equivalent emitter resistance,

𝑟′𝑒 is the dynamic base-emitter junction resistance.

The final negative sign indicates that the collector voltage at transistor number 1 is 180 degrees out of phase with the input signal. Earlier, we noted that 𝑖𝐸2 is the same magnitude as 𝑖𝐸1 , the only difference being that it is out of phase. Because of this, the magnitude of the collector voltage at transistor number 2 will be the same as that on the first transistor. Because the second current is out of phase with the first, it follows that the second collector voltage must be out of phase with the first. This means that the voltage at the second collector is in phase with the first input signal. Its gain Equation is

![]()

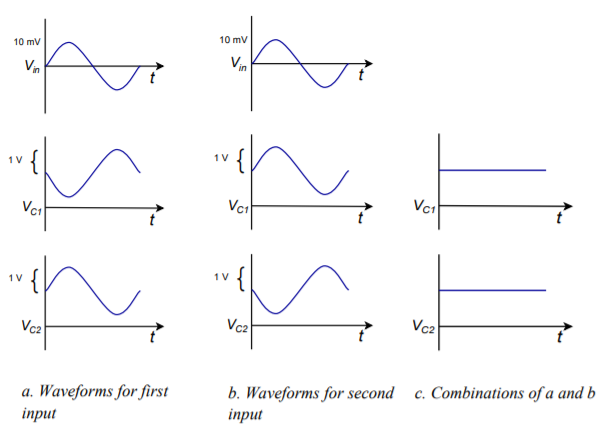

The various waveforms are depicted in Figure 7.6.8 . The preceding Equation is often referred to as the single-ended input/single-ended output gain Equation because it describes the single change from one input to one output. The output signal will be in phase if we are examining the opposite transistor, and out of phase if we are looking at the input transistor. Because the circuit is symmetrical, we will get similar results when we examine the second input. The voltage between the two collectors is 180 degrees apart. If we were to use a differential output, that is, derive the output from collector to collector rather than from one collector to ground, we would see an effective doubling of the output signal. If the reason for this is not clear to you, consider the following. Assume that each collector has a 1 V peak sine wave riding on it. When collector 1 is at +1 V, collector 2 is at -1 V, making +2 V total. Likewise, when collector 1 is at its negative peak, collector 2 is at its positive peak, producing a total of -2 V. The single ended input/differential output gain therefore is

![]()

Example 7.6.2

Using the circuit of Figure 7.6.4 , determine the single-ended input/differential output and single-ended input/single-ended output voltage gains. Use the following component values: 𝑉𝐶𝐶=15𝑉 , 𝑉𝐸𝐸=−8𝑉 , 𝑅𝑇=10𝑘Ω , 𝑅𝐶=8𝑘Ω , 𝑟𝐸=30Ω . In order to find 𝑟′𝑒 we must find the DC current.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

For the single ended output gain,

![]()

![]()

![]()

![]()

The differential output gain is twice this value, or 79.

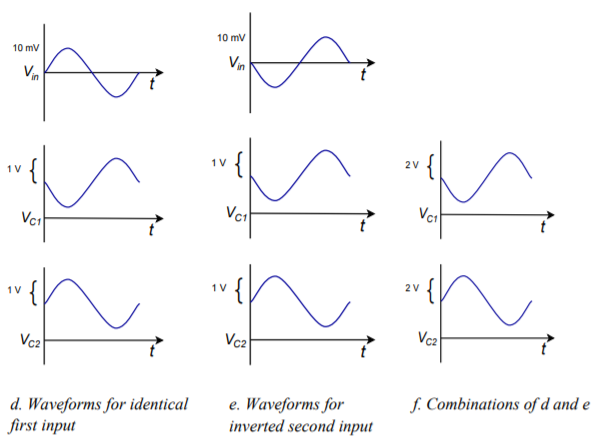

Because it is possible to drive a diff amp with two distinct inputs, a wide variety of outputs may be obtained. It is useful to investigate two specific cases:

- Two identical inputs in both phase and magnitude.

- Two inputs with identical magnitude, but 180 degrees out of phase.

Let’s consider the collector potentials for the first case. Assume that a diff amp has a single-ended input/single-ended output gain of 100 and a 10 mV signal is applied to both bases. Using Superposition, we find that the outputs due to each input are 100 times 10 mV, or 1 V in magnitude. For the first input, the voltages are sketched in Figure 7.6.9𝑎 (following page). For the second input, the voltages are sketched in Figure 7.6.9𝑏 . Note that each collector sees both a sine wave and an inverted sine wave, both of equal amplitude. When these two signals are added, the result is zero, as seen in Figure 7.6.9𝑐. In Equation form,

![]()

![]()

Because 𝑣𝑖𝑛1 and 𝑣𝑖𝑛2 are identical, the output is ideally zero given a perfectly matched and biased diff amp. The exact same effect is seen on the opposite collector. This last Equation is very important. It says that the output voltage is equal to the gain times the difference between the two inputs. This is how the differential amplifier got its name. In this case, the two inputs are identical, and thus their difference is zero. On the other hand, if we were to invert one of the input signals (case 2), we find a completely different result.

![]()

![]()

![]()

![]()

Thus, if one input is inverted, the net result is a doubling of gain. This effect is shown graphically in Figures 7.6.9𝑑 through 7.6.9𝑓 . In short, a differential amplifier suppresses in phase signals while simultaneously boosting out of phase signals. This can be a very useful attribute, particularly in the area of noise reduction.

Common Mode Rejection

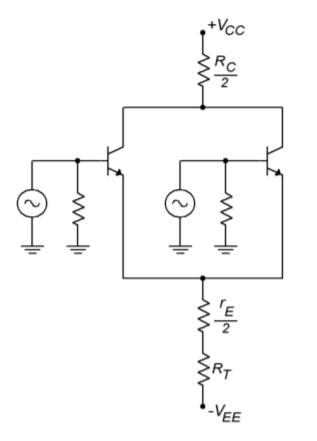

By convention, in phase signals are known as common-mode signals. An ideal differential amplifier will perfectly suppress these common-mode signals, and thus, its common-mode gain is said to be zero. In the real world, a diff amp will never exhibit perfect common-mode rejection. The common-mode gain may be made very small, but it is never zero. For a common-mode gain of zero, the two halves of the circuit have to be perfectly matched, and all circuit elements must be ideal. This is impossible to achieve as errors may arise from several sources. The most obvious error sources are resistor tolerance variations and transistor parameter spreads. The basic design of the circuit will also affect the common-mode gain. With some circuit rearrangements, it is possible to determine a common-mode gain for the circuits we have been using. The circuit of Figure 7.6.4 has been redrawn in Figure 7.6.10 in order to emphasize its parallel symmetry.

Because the DC potentials are identical in both halves, and identical signals drive both inputs, we can combine resistors in parallel in order to arrive at the circuit of Figure 7.6.11 .

Although it is not shown explicitly on the diagram, the internal dynamic resistances (𝑟′𝑒) may also be combined ( 𝑟′𝑒/2 ). This circuit has been effectively reduced to a simple common emitter stage. Based on our earlier work, the gain for this circuit is

![Rendered by QuickLaTeX.com \[A_{v(cm)} = \frac{\frac{r_C}{2}}{R_T + \frac{r^{'}_e}{2} + \frac{r_E}{2}} \]](https://pressbooks.nscc.ca/app/uploads/quicklatex/quicklatex.com-025c66011f830a1c57913b2febf2e1c6_l3.png)

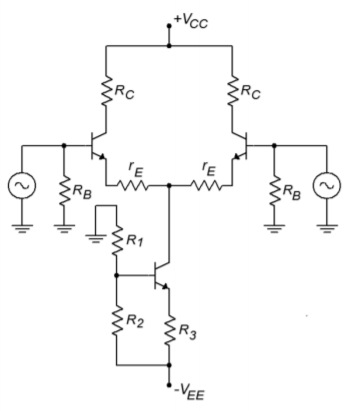

This is the common-mode voltage gain. If 𝑅𝑇 is considerably larger than 𝑟𝐶 , then this circuit will exhibit good common mode rejection (assuming that the other parts are matched, naturally). 𝑅𝑇 is the effective resistance of the tail current source. A very high internal resistance (i.e., an ideal current source) is desirable. There are many ways of creating a more ideal current source. One way is to use a third bipolar transistor as shown in Figure 7.6.12 .

The tail current is found by determining the potential across 𝑅2 and subtracting the 0.7 V 𝑉𝐵𝐸 drop. The remaining potential appears across 𝑅3 . Given the voltage and resistance, Ohm’s Law will let you find the tail current. In this circuit, 𝑅2 is sometimes replaced with a Zener diode. This can help to reduce temperature induced current fluctuations. In any case, the effective resistance of this current source is considerably larger than the simple tail resistor variation. It is largely dependent on the characteristics of the tail current transistor, and can easily be in the megohm region.

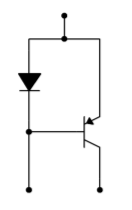

Current Mirror

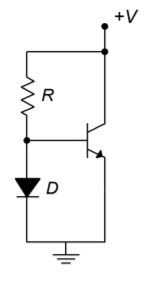

A very popular biasing technique in integrated circuits involves the current mirror. Current mirrors are also employed as active loads in order to optimize a circuit’s gain. A simple current mirror is shown in Figure 7.6.13 . This circuit requires that the transconductance curves of the diode and the transistor be very closely matched. One way to guarantee this is to use two transistors, and form one of them into a diode by shorting its collector to its base. If we use an approximate forward bias potential of 0.7 V and ignore the small base current, the current through the diode is

![]()

In reality, the diode potential will probably not be exactly 0.7 V. This will have little effect on 𝐼𝑑 though. Because the diode is in parallel with the transistor’s base-emitter junction, we know that 𝑉𝑑=𝑉𝐵𝐸 . If the two devices have identical transconductance curves, the transistor’s emitter current will equal the diode current. You can think of the transistor as mirroring the diode’s current, hence the circuit’s name. If the two device curves are slightly askew, then the two currents will not be identical. This is shown graphically in Figure 7.6.14 .

Example 7.6.3

A current mirror could be used in the circuit of Figure 7.6.12 . The result is shown in Figure 7.6.15 . If the positive power supply is 15 V, the negative supply is -10 V, and 𝑅 is 10 k\Omega, the tail current will be

![]()

![]()

![]()

Because the tail current is the mirror current,

![]()

![]()

Biasing of this type is very popular in operational amplifiers. Another use for current mirrors is in the application of active loads. Instead of using simple resistors for the collector loads, a current mirror may be used instead. A PNP based current mirror suitable for use as an active load in our previous circuits is shown in Figure 7.6.16 .

To use this, we simply remove the two collector resistors from a circuit such as Figure 7.6.15 , and drop in the current mirror. The result of this operation is shown in Figure 7.6.17 . The current mirror active load produces a very high internal impedance, thus contributing to a very high differential gain. In effect, by using a constant current source in the collectors, all AC current is forced into the following stage. You may also note that the number of resistors used in the circuit has decreased considerably.