4.3 MOSFET Common Drain Followers

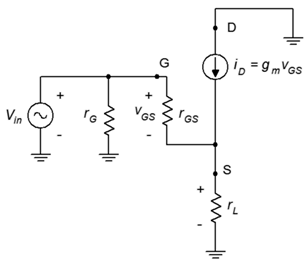

As discussed under the section on JFETs, the common drain amplifier is also known as the source follower. The prototype amplifier circuit with device model is shown in Figure 4.3.1 . As with all voltage followers, we expect a non-inverting voltage gain close to unity with a high 𝑍𝑖𝑛 and a low 𝑍𝑜𝑢𝑡 .

As is usual, the input signal is applied to the gate terminal and the output is taken from the source. Because the output is at the source, biasing schemes that have the source terminal grounded, such as zero bias and voltage divider bias, cannot be used.

Voltage Gain

The voltage gain equation for the common drain follower is developed as follows: We begin with the fundamental definition that voltage gain is the ratio of 𝑣𝑜𝑢𝑡 to 𝑣𝑖𝑛 , and proceed by expressing these voltages in terms of their Ohm’s law equivalents. The load is now located at the MOSFET’s source, and thus can be referred to as either 𝑟𝐿 or 𝑟𝑆 .

![]()

![]()

![]()

![]()

(4.3.1)

or, if preferred

![]()

If 𝑔𝑚𝑟𝑆≫1 , the voltage gain will be very close to unity; a desired outcome.

Input Impedance

The analysis for source follower’s input impedance is virtually identical to that for the common source amplifier. The same commentary applies regarding the simplification of gate biasing resistors to arrive at the value of 𝑟𝐺 .

![]()

(4.3.3)

Output Impedance

In order to determine the output impedance, we modify the circuit of Figure 4.3.1 by separating the load resistance from the source bias resistor. This is shown in Figure 4.3.2 .

Looking back into the source from the perspective of the load we find that the source biasing resistor, 𝑅𝑆, is in parallel with the impedance looking back into the source terminal.

![]()

To find 𝑍𝑠𝑜𝑢𝑟𝑐𝑒 , note that the voltage at the source is 𝑣𝐺𝑆 and the current entering this node is 𝑖𝐷 . The ratio of the two will yield the impedance looking back into the source.

![]()

![]()

![]()

(4.3.4)

Therefore, the output impedance is

![]()

(4.3.5)

Looking at Equation 4.3.5 it is obvious that the higher the transconductance, the lower the output impedance. As noted earlier, a large transconductance also means that the voltage gain will be close to unity. As a general rule then, a large transconductance is desired for the source follower.

Time for a few illustrative examples.

Example 4.3.1

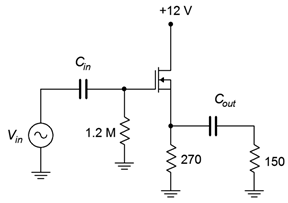

For the circuit of Figure 4.3.3 , determine the voltage gain and input impedance. Assume 𝑉𝐺𝑆(𝑜𝑓𝑓) = −0.8 V and 𝐼𝐷𝑆𝑆 = 30 mA.

This amplifier uses self bias so we need to determine 𝑔𝑚0𝑅𝑆 .

![]()

![]()

![]()

The DC source resistance is the 270 Ω biasing resistor resulting in 𝑔𝑚0𝑅𝑆 = 16.2. From the self bias equation or graph this produces a drain current of 2.61 mA.

![]()

![]()

![]()

The voltage gain is

![]()

![]()

![]()

Finally, for the input impedance we have

![]()

Example 4.3.2

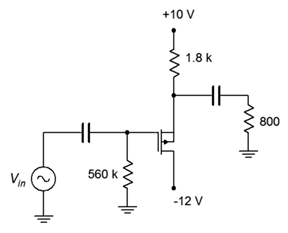

For the circuit of Figure 4.3.4 , determine the voltage gain and input impedance. Assume 𝑉𝐺𝑆(𝑜𝑓𝑓) = −2.5 V and 𝐼𝐷𝑆𝑆 = 80 mA.

This follower uses a P-channel device with combination bias. Note that the source terminal is toward the top of the schematic. First, determine 𝑔𝑚0𝑅𝑆 and the bias factor, 𝑘 . Then the combination bias equation can be used to determine the drain current.

![]()

![]()

![]()

The DC source resistance is the 1.8 k Ω biasing resistor resulting in 𝑔𝑚0𝑅𝑆 = 115.2. The bias factor is 𝑉𝑆𝑆/𝑉𝐺𝑆(𝑜𝑓𝑓) , or 4. The combination bias equation (Equation 10.9) yields 𝐼𝐷 = 6.67 mA.

We can now find the transconductance and voltage gain.

![]()

![]()

![]()

The voltage gain is

![]()

![]()

![]()

Lastly, the input impedance is

![]()