4.2 MOSFET Common Source Amplifiers

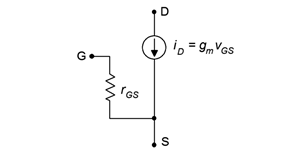

Before we can examine the common source amplifier, an AC model is needed for both the DE- and E-MOSFET. A simplified model consists of a voltage-controlled current source and an input resistance, 𝑟𝐺𝑆. This model is shown in Figure 4.2.1 . The model is essentially the same as that used for the JFET. Technically, the gate-source resistance is higher in the MOSFET due to the insulated gate, and this is useful in specific applications such as in the design of electrometers, but for general purpose work it is a minor distinction. The impedance associated with the current source is not shown as it is typically large enough to ignore. Similarly, the device capacitances are not shown. It is worth noting that the capacitances associated with small signal devices might be just a few picofarads, however, a power device might exhibit values of a few nanofarads.

As the device model is the same for both DE- and E-MOSFETs, the analysis of voltage gain, input impedance and output impedance will apply to both devices. The only practical differences will be how the transconductance is determined, and circuit variations due to the differing biasing requirements which will effect the input impedance. In fact, there will be a great uniformity between JFET-based circuits and DE-MOSFET circuits operating in depletion mode.

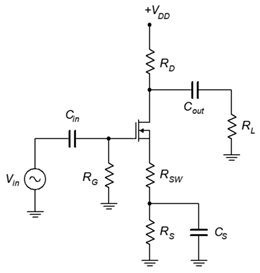

An AC equivalent of a swamped common source amplifier is shown in Figure 4.2.2 . This is a generic prototype and is suitable for any variation on device and bias type. Ultimately, all of the amplifiers can be reduced down to this equivalent, occasionally with some resistance values left out (either opened or shorted). For example, if the amplifier is not swamped then 𝑟𝑆=0 . Similarly, 𝑟𝐺 might correspond to a single gate biasing resistor or it might represent the equivalent of a pair of resistors that set up a gate voltage divider.

Voltage Gain

In order to derive an equation for the voltage gain, we start with its definition, namely that voltage gain is the ratio of 𝑣𝑜𝑢𝑡 to 𝑣𝑖𝑛. We then proceed by expressing these voltages in terms of their Ohm’s law equivalents. Note that 𝑟𝐿 can also be called 𝑟𝐷.

![]()

![]()

![]()

![]()

(4.2.1)

or, if preferred

![]()

(4.2.2)

This is the general equation for voltage gain. If the amplifier is not swamped then the first portion of the denominator drops out and the gain simplifies to

![]()

(4.2.3)

or alternately

![]()

(4.2.4)

The swamping resistor, 𝑟𝑆, plays the same role here as it did with both the BJT and JFET. Swamping helps to stabilize the gain and reduce distortion, but at the expense of voltage gain.

Input Impedance

Referring back to Figure 4.2.2 , the input impedance of the amplifier will be 𝑟𝐺 in parallel with the impedance looking into the gate terminal, 𝑍𝑖𝑛(𝑔𝑎𝑡𝑒). At a minimum this will be 𝑟𝐺𝑆 (it is somewhat higher when swamped but this can be ignored in most cases). At low frequencies 𝑟𝐺𝑆 is very large, perhaps as high as 1012 ohms. In most practical circuits, 𝑟𝐺 will be much lower, hence

![]()

(4.2.5)

It is important to reiterate that 𝑟𝐺 is the equivalent resistance seen prior to the gate terminal that is seen from the vantage point of 𝑉𝑖𝑛. In the case of self bias, combination bias, zero bias and constant current bias, this will be the single biasing resistor 𝑅𝐺. For simple voltage divider biasing, 𝑟𝐺 will be the parallel combination of the two divider resistors (i.e., 𝑅1||𝑅2). For decoupled voltage divider biasing, as shown in Figure 4.2.3 , 𝑟𝐺 will be the decoupling resistor (i.e., 𝑅3 ) that is connected between the divider and the gate. This is because the divider node is bypassed to ground via a capacitor. Finally, for drain feedback biasing, 𝑟𝐺 is the Millerized 𝑅𝐺 that bridges the drain and gate.

Output Impedance

The derivation of output impedance is unchanged from the JFET case. From the perspective of the load, the output impedance will be the drain biasing resistor, 𝑅𝐷, in parallel with the internal impedance of the current source within the device model. 𝑅𝐷 tends to be much lower than this, and thus, the output impedance can be approximated as 𝑅𝐷.

Therefore we may state

![]()

(4.2.6)

At this point, a variety of examples are in order to illustrate some of the myriad combinations.

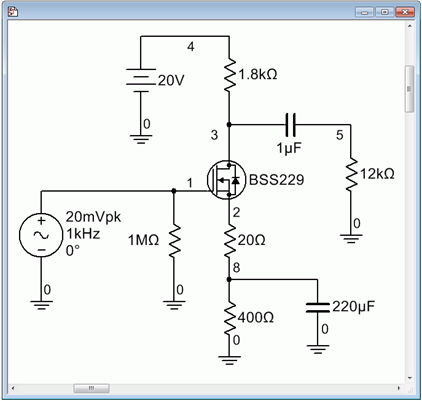

Example 4.2.1

For the amplifier in Figure 4.2.4 , determine the input impedance and load voltage. 𝑉𝑖𝑛 = 20 mV, 𝑉𝐷𝐷 = 20 V, 𝑅𝐺 = 1 M Ω , 𝑅𝐷 = 1.8 k Ω , 𝑅𝑆𝑊 = 20 Ω , 𝑅𝑆 = 400 Ω , 𝑅𝐿 = 12 k Ω , 𝐼𝐷𝑆𝑆 = 40 mA, 𝑉𝐺𝑆(𝑜𝑓𝑓) = −1 V.

This is a swamped common drain amplifier utilizing self bias. 𝑍𝑖𝑛 can be determined via inspection.

![]()

![]()

To find the load voltage we’ll need the voltage gain, and to find the gain we’ll first need to find 𝑔𝑚0.

![]()

![]()

![]()

The combined DC value of 𝑅𝑆 is 420 Ω , therefore 𝑔𝑚0𝑅𝑆 = 33.6. From the self bias equation or graph this produces a drain current of 1.867 mA.

![]()

![]()

![]()

The swamping resistor, 𝑟𝑆 , is 20 Ω . The voltage gain is

![]()

![]()

![]()

And finally

![]()

![]()

![]()

Computer Simulation

The amplifier of Example 4.2.1 is simulated to verify the results. The circuit is entered into the simulator as shown in Figure 4.2.5 . One issue is finding an appropriate DE-MOS device to match the parameters used in the example. The BSS229 proves to be reasonably close. This device model was tested for 𝐼𝐷𝑆𝑆 by applying a 20 volt source to the drain and shorting the source and gate terminals to ground in the simulator. The current was just under the 40 mA target. Similarly, a negative voltage was attached to the gate and adjusted until the drain current dropped to nearly zero in order to determine 𝑉𝐺𝑆(𝑜𝑓𝑓) . The model’s value was just under the desired −1 volt. Consequently, we can expect the simulation results to be close to those predicted, although not identical.

The transient analysis is run next and is shown in Figure 4.2.6 . The expected signal inversion is obvious. The peak amplitude is 417 mV, just a few percent higher than the calculated value. At least some of this deviation is due to the model’s variation from the assumed device parameter values.

A DC bias check is also performed. The drain current was calculated to be 1.867 mA. This yields an 𝑅𝐷 voltage of a little over 3 volts, thus we expect to see a drain voltage of about 17 volts. Similarly, we would expect the source terminal to be sitting at around 700 to 800 mV and the gate at about 0 V.

The results of the DC operating point simulation are shown in Figure 4.2.7 . The agreement with the predicted values is quite good, especially considering that the device model is not a perfect match.

Example 4.2.2

For the circuit of Figure 4.2.8 , determine the voltage gain and input impedance. Assume 𝑉𝐺𝑆(𝑡ℎ) = 2 V, 𝐼𝐷(𝑜𝑛) = 50 mA at 𝑉𝐺𝑆(𝑜𝑛) = 5 V.

First find the value of 𝑘 :

![]()

![]()

![]()

This circuit uses power supply decoupling. The voltage drop across the 2 M Ω resistor is small enough to ignore as the current passing through it is gate current. Therefore the gate voltage is determined by the divider. Also, as the left end of the 2 M Ω resistor is tied to an AC ground due to the bypass capacitor, it represents the input impedance.

![]()

![]()

![]()

![]()

The source is grounded so 𝑉𝐺𝑆=𝑉𝐺 .

![]()

![]()

![]()

![]()

![]()

![]()

This amplifier is not swamped so the simplified gain equation may be used.

![]()

![]()

![]()

Example 4.2.3

For the circuit of Figure 4.2.9 , determine the voltage gain and input impedance. Assume 𝑉𝐺𝑆(𝑜𝑓𝑓) = −0.75 V and 𝐼𝐷𝑆𝑆 = 6 mA.

This amplifier uses zero bias, therefore 𝐼𝐷=𝐼𝐷𝑆𝑆 and 𝑔𝑚=𝑔𝑚0 .

![]()

![]()

![]()

This amplifier is not swamped so we may use the simplified equation for voltage gain.

![]()

![]()

![]()

Finally, for the input impedance we have

![]()